上海2014年7月7日电 /美通社/ -- 电子设计自动化技术的领导厂商 Mentor Graphics近日发布一份题为《硅光子带来新的设计挑战》的研究报告。中文版的报告全文可在 Mentor Graphics 的官方网站阅读和下载:http://mentorg.com.cn/aboutus/view.php?id=263。

作者:John Ferguson 和 Fedor Pikus, Mentor Graphics公司

新兴硅光子 (SiP) 技术前景广阔,有望带来显著的性能提升和可控制的生产成本。光信号传播速度较快,而且没有物理寄生造成的降速影响,这意味着可在极低的功率下实现非常快的处理速度。此外,在成熟的硅工艺(例如体效应互补金属氧化物半导体)中采用光子技术也能带来相对较低的生产成本。但是,随着硅光子设计从研究阶段进入商业生产,光子设计人员在完全实现这些好处之前必须掌握一些新的设计规则。本文讨论了一些在使用成熟的集成电路 (IC) 工艺生产时确保硅光子电路表现达到预期的较佳方法。

传统的设计和验证流程

在传统的集成电路工艺中,设计人员通常会使用原理图捕获工具,按照预想的电气性能创建一个设计。接着,他们使用代工厂SPICE模型来仿真电路性能,确保达到预想的功能。最后,他们会创建一个版图来实现原理图设计。这个版图必须符合工艺设计规则,这可以通过将设计版图(通常采用GDSII等格式)传递至设计规则检查(DRC)工具进行确认。DRC确保设计方案可以生产出来,但不能确保硅的实际表现符合设计意图和仿真结果。要想做到这一点,可使用版图与原理图 (LVS) 对比流程来验证物理电路设计。LVS流程可阅读物理版图,提取出一个以SPICE电路表示法来描绘电气结构的网表。然后将这个提取出的网表与原始的网表进行比较。如果二者相匹配,那么设计人员便可确信版图既能生产出来,又能达到预期性能。代工厂为设计人员提供专为某个特定节点和工艺服务的DRC平台、SPICE设备模型和LVS平台。

硅光子的挑战

然而,这个工艺流程并不适用于硅光子。虽然SiP设计与定制模拟集成电路设计有很多相似之处,但挑战存在于细节方面。虽然 SiP 设计也在很大程度上依赖早期设计仿真,但SPICE不具备模拟光学器件所需的尖端技术。光子设计人员必须使用其它建模和仿真工具,与SPICE不同,SiP行业标准尚未确立,这些工具未必能够与集成电路领域使用的工具进行互操作。较值得一提的是,这些仿真器没有使用标准SPICE 网表的概念,因此,传统LVS工具无法对比这些仿真器提取出的网表。

光子电路LVS的另一个复杂之处在于器件的特殊性。LVS流程通常历经三个阶段:版图中的器件识别、器件的特性鉴定以及器件连接和参数与原理图的对比。第一步的挑战相对较小,因为光子器件的外形很容易辨认。但是,外形的复杂性使器件的特性鉴定变得十分困难。光子器件的性能取决于器件复杂外形的很多细节以及周边布局。

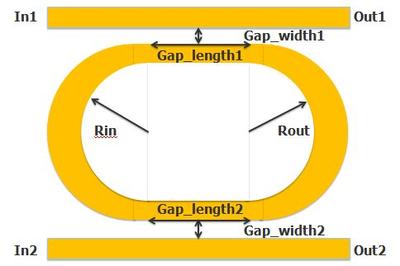

图1显示了一个简单的环形谐振器器件。共有四个管脚:In1、In2、Out1 和 Out2。有六个参数(均可以独立地变化)对该器件的性能至关重要:Rin、Rout、Gap_length1、Gap_width1、Gap_length2 和 Gap_width2。如果有任何参数与目标值不同,器件将无法达到预期性能。鉴于Rin和Rout的曲线特性,很难以GDSII直线格式(使用一系列分段线性直线)来准确描绘设计。因此会出现半径不准确的严重情况,从而造成功能问题。

在LVS中,传统的器件特性鉴定方法是收集器件周围可能影响其性能的所有布局对象,通过测量来描述这些对象和器件本身之间的相互作用,例如距离和投影长度。这些测量结果可以按照第一原则理论或硅测量经验曲线代入封闭公式。但是,当器件受很多特征影响或者一些简单的测量无法足够准确地捕捉物体之间的相互作用(光子器件就是这样)时,这种方法便不再奏效。这种情况与模拟电路设计人员所面临的问题很像,除了器件本身形成的少数对象,器件性能有时还取决于数千个布局对象共同的电容和电感。

设计流程调整

我们提议放弃基于精确测量的特性鉴定,代之以一系列周知的模式来识别器件,包括主要的器件特征和周边一定范围内的版图形状。这些器件可以使用硅测量或现有的硅光子仿真器进行预特性化(与面向集成电路设计的技术计算机辅助设计(TCAD)器件仿真类似)。如有必要,这种模式还可以引入少量的变异度,但重要的是,版图中的器件必须与预特性化模式之一完全匹配。当设计人员在版图中实施这些预特性化器件时,LVS工具可以抽取器件、测量其重要参数并且将他们与预特性化模式相比较。模式库里未发现的任何器件会被标记成未知器件,并被视作版图错误处理。

光子电路LVS验证的另一个挑战源于电路比较阶段。大多数LVS工具的开发都基于这样的假设:对版图的分析可以依赖常见数据库中描述的单个CMOS传输门的逻辑属性。光子电路的基本元素如谐振器、调制器和多路器存在很大区别。在硅光子更加成熟之前,普通的LVS工具不可能像支持MOSFET和CMOS传输门一样的按照“原始器件”支持所有基本的光器件。相反,LVS工具必须支持用户定义器件和电路模式。验证器件参数还需要更大的灵活性,一些参数适用于整个器件,而另一些则与特定器件引脚或多个引脚相关(例如一个特定波导在一个多路器中的传输与对话)。与“标准的”传输门不同,电路的模式驱动型识别是分离具有特定功能的元素所必需的。

从概念上讲,这个方法与通常应用于模拟器件特性鉴定问题的解决方案类似:这些设备的确切性能特性十分复杂,并且通常很少为人所知。设计人员通常缺乏具有几个著名参数的准确压缩模型。相反,在一个相对较大的版图环境下,许多几何形状的复杂互动决定了器件性能。对于光子器件来说,情形极其类似。光子器件的性能由组成器件的许多布局类型的精美细节决定。细节会受到按照GDS多边形绘制几何的平滑曲线时的制品的影响,然后进一步分裂成适合掩膜制造机器的元素,最终被光刻生产工艺所扭曲。因此,只通过几个与其规模和大小相关的参数对器件进行可靠的特性鉴定并不现实。LVS 工具必须将这些器件与一个已知的良好且优秀的配置变体库进行比较。当发现匹配项时,性能参数可以直接从库项目中提取。“类似”但是并不完全匹配任何库变量的器件应该被标记为警告信息。

总结

当LVS工具能够发现和提取具有复杂曲线形状的用户定义器件时,硅光子设计人员可以从真正的LVS验证中获得信心,并且提取适当的物理测量器件参数,用于与一个仔细预特性化设备库进行对比。使用这个方法,既定的器件到器件行为可以进行验证,确保不存在意外的短路或开路。通过仔细验证如图所示器件参数与预期的预特性化性能相匹配,电路中每个器件的预期性能得到了进一步的确保。也许重要的是,意外的设计错误会在结构完好的设计环境中被及早发现并通知用户,从而快速简单地排除故障,节省不必要的生产周期并且大大缩短上市时间。

作者介绍

John Ferguson 是总部位于俄勒冈州威尔森维尔的明导 Calibre DRC Applications 的营销总监。他在1991年获得麦吉尔大学 (McGill University) 物理学学士学位,1993年获得马萨诸塞大学 (University of Massachusetts) 应用物理硕士学位,2000年获 Oregon Graduate Institute of Science and Technology 电气工程博士学位。John 在面向前沿的集成电路生产制造的物理设计验证领域拥有丰富的工作经验。

Fedor Pikus 是明导 Design to Silicon 部门首席工程科学家。他之前的职位包括谷歌高级软件工程师以及明导 Calibre PERC, LVS, DFM 首席软件架构师。他于1998年加盟明导,从计算物理学学术研究转至软件行业。作为首席科学家,他的职责包括规划 Calibre 产品的长期技术方向、指导和培养从事这些产品工作的工程师、软件设计与架构以及新设计和软件技术的研究。Fedor 在物理、EDA、软件设计和 C++ 语言方面拥有超过25项专利,发表过超过90篇相关论文与会议报告。